SK海力士推进领先三星的1c DRAM六层EUV工艺创新

据最新消息,SK海力士正在积极推进1c DRAM的六层EUV工艺研发,旨在领先三星等竞争对手,该工艺将有助于提高存储设备的性能和集成度,进一步推动半导体产业的发展,此举引起了业界的高度关注和期待,有望引领新一轮的技术革新和市场竞争。

8 月 12 日消息,科技媒体 wccftech 昨日(8 月 11 日)发布博文,指出 sk 海力士(sk hynix)为提升 ddr5 与高带宽存储(hbm)产品的性能,并在先进存储技术领域保持领先,正计划在 1c dram 的量产中引入六层极紫外光(euv)工艺。

报道称,这一技术方案不仅打破了现有行业规范,还将显著增强 DDR5 与 HBM 存储器的性能表现。根据博文内容,EUV 技术使用波长为 13.5 纳米的光源,能够实现更精密的电路图案刻画,有效减少传统多重曝光(multi-patterning)的需求。

以往 DRAM 制造多结合 EUV 与深紫外光(DUV)技术,而 SK 海力士此次在 1c DRAM 上全面采用六层 EUV 工艺,有助于简化制造流程,同时提升芯片良率与整体盈利能力。

分析认为,在当前存储技术竞争加剧的背景下,SK 海力士的这一举措不仅强化了其在行业内的技术领先地位,也为其在与三星等主要对手的竞争中赢得了新的战略优势。

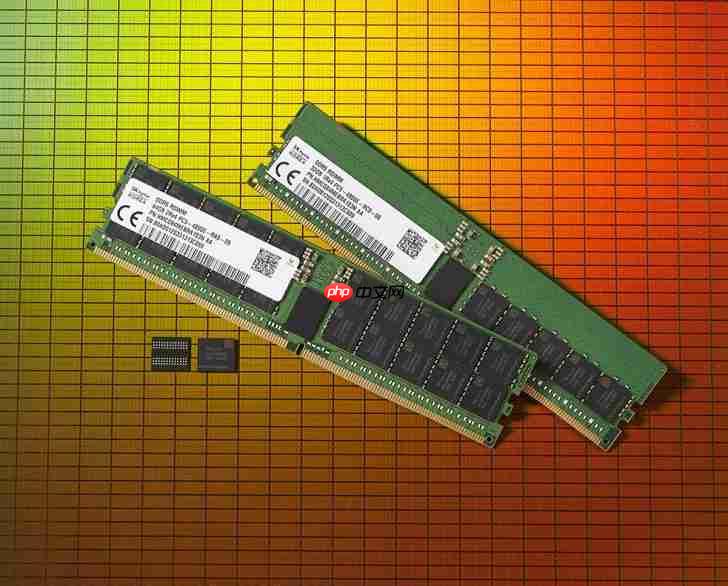

尽管 1c DRAM 尚未大规模进入消费级市场,但 SK 海力士正在积极研究其在高容量 DDR5 及下一代 HBM 产品中的应用潜力。据悉,公司将继续扩大 EUV 工艺的投资,未来将在 1d、0a 等更先进制程节点全面导入 EUV 技术,并逐步向高数值孔径(High-NA)EUV 技术演进。

借助 EUV 工艺的进步,SK 海力士有望制造出密度更高、速度更快、功耗更低的 DDR5 与大容量 HBM 芯片,大幅提升生产效率和产品良率。特别是在 HBM4 等前沿产品中,1c DRAM 的集成预计将实现性能与存储容量的双重飞跃,为人工智能、高性能计算等高需求领域提供更强大的硬件支持。

网友留言(0 条)